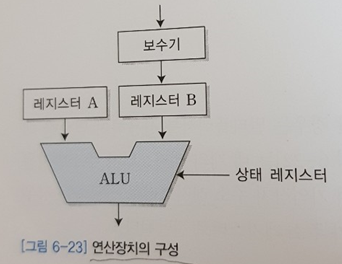

연산장치

- 연산될 데이터와 연산한 결과를 기억시킬 레지스터가 필요

- 연산의 상태를 나타내기 위한 상태 레지스터들의 연결 필요

- 가산기 : 덧셈

- 누산기(AC) : 연산 결과를 일시적으로 저장

- 기억장치 버퍼 레지스터 : 데이터 보관

- 보수기 : 보수를 만듬

- 상태 레지스터 : 계산 결과의 상태를 점검

ALU에서의 연산 회로

①산술연산 회로

- 4개의 전가산기(FA)로 구성된다.

- 병렬 가산기가 여러 가지 연산을 수행하려면 전가산기의 한쪽 입력단자에 논리회로를 추가

- 4개의 전가산기(FA)로 구성된다.

|

선택 신호와 자리 올림 |

출력 |

연산 동작 |

||

|

S1 |

S0 |

Ci |

||

|

0 |

0 |

0 |

F = A |

A를 전송 |

|

0 |

0 |

1 |

F = A + 1 |

A의 증가 캐리를 포함한 덧셈 |

|

0 |

1 |

0 |

F = A + B |

A와 B의 가산 |

|

0 |

1 |

1 |

F = A + B + 1 |

A와 B의 캐리 가진 가산 |

|

1 |

0 |

0 |

F = A + B’ |

A와 B의 1의 보수 가산 |

|

1 |

0 |

1 |

F = A + B’ + 1 |

감산(A와 B의 2의 보수 덧셈) |

|

1 |

1 |

0 |

F = A – 1 |

A를 1감소 |

|

1 |

1 |

1 |

F = A |

A를 전송 |

②논리연산 회로

- 논리 게이트들을 이용항 조합 논리회로를 구성하면 다양한 논리연산을 수행할 수 있다.

- 입력되는 데이터 A와 B의 내용을 연산 지시에 의해 AND, OR, XOR 및 NOT연산을 수행할 수 있다.

- 논리 게이트의 조합 논리회로와 이들을 선택할 수 있는 멀티플렉서로 구성되어 있다.

- 4 X 1 멀티플렉서는 4개의 논리연산이 선택 선S1과 S0에 의해서 하나가 선택되고 출력하게 한다.

③ALU

- 설계된 산술연산 회로와 논리연산 회로를 조합하면 ALU가 완성된다.

- 선택 선 S1과 S0는 산술연산 회로와 논리연산 회로가 공통으로 사용하고, 또 하나의 선택 선 S2는 두 회로 중 하나를 선택하는데 사용

- S2가 0이면 산술연산, S2가 1이면 논리연산 수행

상태비트

- 플래그(flag)나 조건 코드라고 불린다.

- 자리올림(C:carray), 부호(S:sign), 제로(Z:zero), 오버플로우(V:overflow) 네가지가 필수적이다.

- 오버플로우 비트를 동작하려면 XOR게이트 필요

- 제로 비트를 동작하려면 NOR게이트 필요

-C : 자리 올림 비트가 1이면 자리 올림수가 발생한 것

-S : 부호 비트가 1이면 음수, 0이면 양수

-Z : 결과의 모든 출력이 0이면 제로 비트는 1, 그렇지 않으면 0

-V : ALU의 두자리 올림수 C8, C9를 XOR한 결과가 1이면 오버플로우 발생, 0이면 오버플로우 발생하지 않은 것

이동회로(shifter)

- 이동기는 이동 레지스터라고도 한다.

- 이동기에서 이동방향은 좌측과 우측이다.

- 이동할 때 이동 방향의 마지막 비트 값은 바깥으로 밀려난다.

- 반대편의 처음 비트는 상대적을 공백이 생기는데 이곳에 0이나 1이 채워진다.

728x90

반응형

'컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조 - CPU의 기능과 동작 (0) | 2019.11.07 |

|---|---|

| 컴퓨터구조 - CPU의 논리회로 설계(제어장치) (0) | 2019.11.07 |

| 컴퓨터구조 - CPU의 논리회로 설계(레지스터) (0) | 2019.11.07 |

| 컴퓨터구조 - CPU의 논리회로 설계 (0) | 2019.11.07 |

| 컴퓨터구조 - 내부 CPU 버스 (0) | 2019.11.07 |