레지스터의 설계

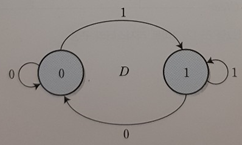

- D 플립플롭은 레지스터를 제작하는 구성 요소 사용

- 입력 신호 D가 클록 펄스에 동기되어 그댈 출력에 전달

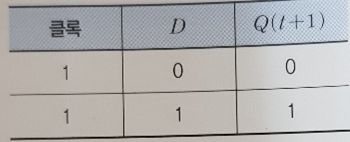

4비트 레지스터

- 각 플립플롭은 공통의 클록을 가지고 있다.

- 클록이 플립플롭에 입력될 때마다 4비트의 입력 I0 ~ I3가 저장되며, 출력 측 A0 ~ A3은 저장된 값을 참조

레지스터의 전송

①레지스터 간 전송

- 직렬 전송 방식

- 1비트씩 이웃한 플립플롭 회로로 이동하고 가장 끝의 플립플롭은 또 다른 레지스터의 플립플롭을 전송

- 이동 레지스터(shift register)라고 한다.

- 전송하는 레지스터의 내용을 보존하려면 직렬 출력을 다시 직렬로 입력하여 모든 비트가 원래의 위치에 있어야 한다. - 병렬 전송 방식

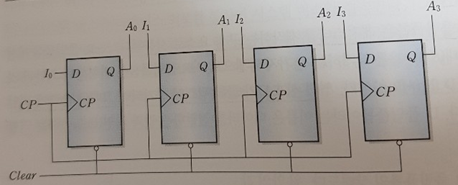

- 레지스터에 기억된 전체 내용을 하나의 제어신홀 다른 레지스터에 동시에 전송되는 방식 - 4비트 레지스터 병렬 전송

로드가 0인 경우 I0 ~ I3의 입력은 차단, 플립플롭의 결과가 다시 플립플롭으로 입력

②버스 전송 방식

- 병렬 버스 전송 : 버스 내 선의 개수와 레지스터를 구성하는 플립플롭의 개수가 일치

- 단일 버스 전송 : 버스로 사용하는 회선이 한 개이므로 1비트 신호인 제어신호를 전송하거나 직렬 전송만이 가능하다.

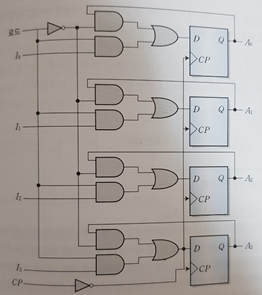

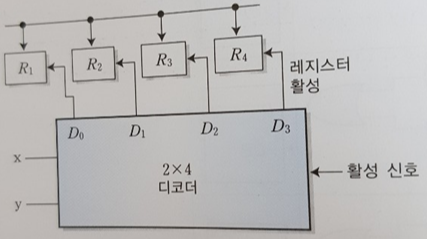

•디코더를 활용한 단일 버스 연결

- 레지스터 네 개에서 단일 버스를 통해 데이터를 공동을 전송하고자 하는 경우

- 레지스터를 선택하기 위해 2비트가 입력되는 디코더를 사용

- 4개의 레지스터 R1 ~ R4가 디코더에 연결

- 선택 신호 X와 Y가 디코더에서 D0 ~ D3의 출력 중 하나를 선택하여 거기에 연결된 레지스터 활성화

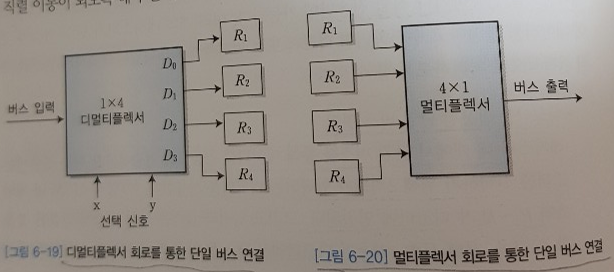

•멀티플렉서와 디멀티플렉서의 단일 버스 연결

- 단일 버스가 수신되는 방법

- 디멀티플렉서 회로를 사용

- 선택 신호에 의해 디멀플렉서 회로의 출력 D0 ~ D3가 생성되므로 직접 레지스터에 연결

- 단일 버스가 송신 되는 방법

- 멀티플렉서 회로를 사용

- x와 y가 지적하는 회로에 의해 R1 ~ R4 중 하나가 선택되고, 선택된 레지스터는 버슬 데이터를 출력

③기억장치 전송 방식

- 기억장치 주소 레지스터와 기억장치 버퍼 레지스터가 필요하다.

- 기억장치 주소 레지스터 : 주소 번지 저장

- 기억장치 버터 레지스터 : 주기억장치에서 읽거나 기록할 때 임시저장

728x90

반응형

'컴퓨터구조' 카테고리의 다른 글

| 컴퓨터구조 - CPU의 논리회로 설계(제어장치) (0) | 2019.11.07 |

|---|---|

| 컴퓨터구조 - CPU의 논리회로 설계(연산장치) (0) | 2019.11.07 |

| 컴퓨터구조 - CPU의 논리회로 설계 (0) | 2019.11.07 |

| 컴퓨터구조 - 내부 CPU 버스 (0) | 2019.11.07 |

| 컴퓨터구조 - 제어장치 (0) | 2019.11.07 |